첨단 반도체 패키징 기술 개발 및 표준화 동향

최근 반도체 기술은 소자의 물리적 한계 및 공정 미세화 기술뿐 아니라 고도의 설계기술이 요구되는 등그 패러다임이 변화하고 있다. 이에 따라 다양한 첨단 반도체 패키징 기술의 연구개발은 물론 관련 시장 선점 혹은 확보를 위한 기업들의 행보가 점점 더 치열해지는 추세를 보인다. 특히 4차 산업의 시장 변화로 인공지능, IoT, 자율주행, 빅데이터 등 고성능·고밀도 시스템의 발전을 위해서는 반도체 패키징 기술 개발과 선점이 매우 중요하다고 할 수 있다.

반도체의 기능이 복잡하고 다양해짐에 따라 신호 핀 수가 증가하는 것은 물론 성능향상의 병목현상이 패키지에서 발생하고 있기 때문이다. 따라서 반도체 패키지의 성능향상이 소자 및 회로의 성능향상 못지않게 중요한 분야로 대두되고, 이를 달성하기 위한 신개념의 패키지 기술이 요구되고 있다. 궁극적으로 반도체 패키지 산업은 소자의 고성능화, 고기능화를 위한 차세대 반도체의 방안으로 중요하게 발전되고 있으며, 초격차 반도체 개발을 위한 필수적인 요소로서 중요성이 증대되고 있는 것이다.

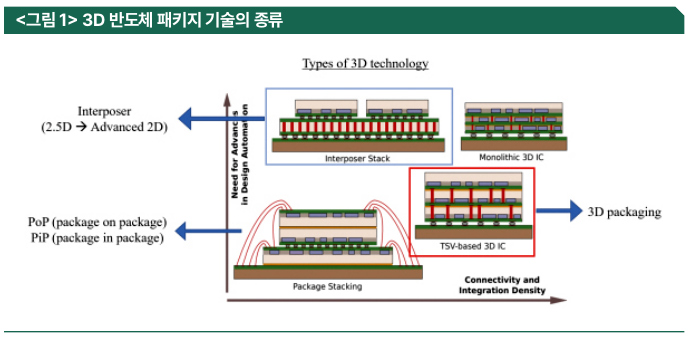

최근 반도체 소자 및 패키징 레벨 전반에 걸쳐 기존의 2D 기술에서 ‘Advanced 2D’ 및 ‘3D 기술’로의 혁신이 진행되고 있으며, 트랜지스터 역시 2D CMOS에서 3D인 ‘FInFET’와 ‘GAA(gate-all-around)’ 로 변화하고 있다. 또한 반도체 패키징 기술에는 패키지된 소자를 적층하는 ▲PoP(package-onpackage) ▲PiP(package-in-package) 기술 ▲Si 또는 재배선(RDL, redistribution layer)을 이용 하는 인터포져(interposer) 기술 ▲Fan-Out 웨이퍼 레벨 기술 ▲소자(칩)를 웨이퍼 레벨이나 칩 레벨로 직접 적층하는 3D 패키징 기술 등 다양한 기술들이 있다. 특히 2019년 IEEE HIR(heterogeneous integration roadmap) 발표 이후 이종집적(HI) 기술은 시스템반도체를 포함한 첨단 패키징 분야의 핵심 기술 방향으로 대두되고 있다.

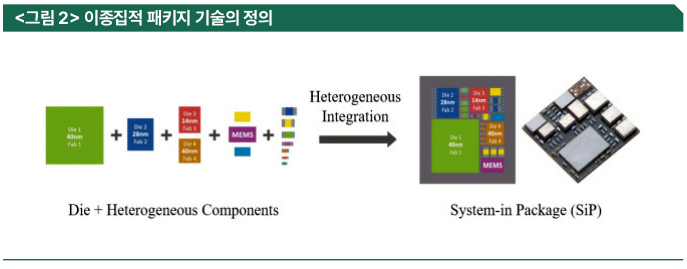

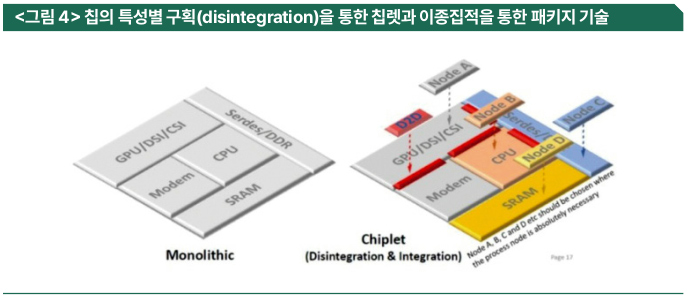

‘이종집적(HI, Heterogeneous Integration)’이란 따로 제작된 다양한 반도체 소자 및 요소들을 하나의 시스템-인-패키지(System-in-Package)로 집적화하는 것을 의미한다. 첨단 패키징(advanced packaging) 기술들을 통해서 시스템의 향상된 기능(functionality)과 작동특성(operating characterstics)을 제공하는 것이다. 이종집적을 적용하는 부품으로는 메모리 및 로직 소자, MEMS 소자, 수동소자, 패키지된 칩 등으로 다양한 소자 및 패키지에 필요한 요소들이 모두 포함된다<그림 1>. 이처럼 이종집적(HI)은 다양한 첨단 반도체패키징 기술을 통해서 이루어지며, ▲FOWLP(fan-out wafer level packaging) ▲die or wafer level 3D packaging ▲2.5D interposer(Advanced 2D) ▲ chiplet 등의 기술이 있다.

이것만은 알아야 할 주요 표준 트렌드

① R&D 관련 표준 동향

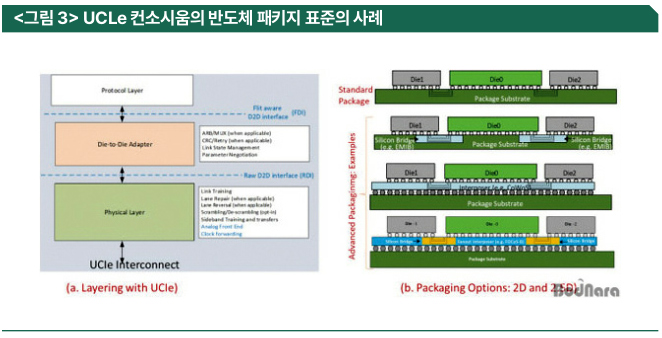

2022년 첨단 반도체 패키지 공정 및 설계의 국제표준화를 위해 AMD, Intel, ARM, ASE, Meta, Google, Qualcomm, Microsoft, 삼성전자 및 TSMC 등 총 10개 회사가 연합한 국제적인 컨소시움인 ‘UCle(Universal Chiplet Interconnect Express)’이 조직됐다. 해당 연합은 단일 패키징 표준을 PCIe, USB, NVMe 등과 같은 새로운 연결 규격으로 수립한다는 목표를 세웠다. 특히 칩렛(Chiplet) 구조를 활용해 호환성과 생산성, 수율 등의 향상 효과를 얻을 수 있을 것으로 기대된다. 참고로 ‘칩렛’ 은 기존의 칩 다이에 탑재된 기능을 분리한 작은 다이를 말한다. 칩렛을 여러 개 붙이는 방식으로 반도체 성능을 높이는 방식이 가격 경쟁력이 있어 최근 이와 같은 칩렛 구조를 채택하는 곳이 증가하고 있다.

② 기술개발에 도움이 되는 주요 표준

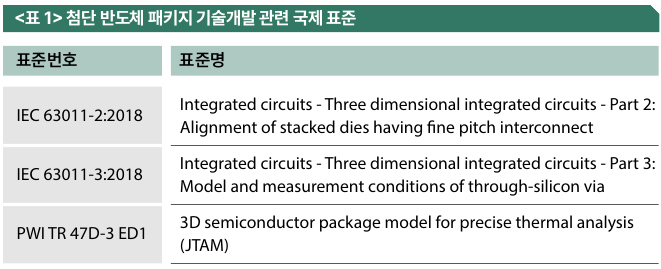

반도체 패키지의 공적 국제표준화를 수행하고 있는 곳은 IEC의 TC 47(Semiconductor devices, 반도체 소자)이며, Subcommittee인 SC 47D (Semiconductor devices packaging, 반도체 소자 패키징) 및 SC 47A(집적회로)에서 주로 수행하고 있다. TC 47에서 첨단 패키징 관련 제정된 표준은 다음과 같다(표 1 참조). 한편 국내에서는 아직 첨단 반도체 관련 국내표준이 제정되지 못하고 있는 실정이다.

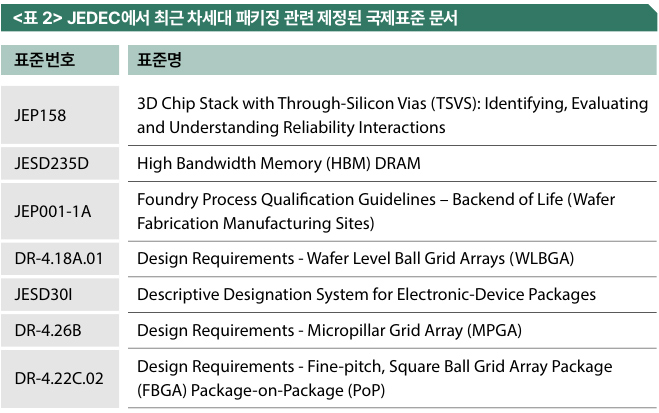

반도체 패키지 기술의 사실상 표준은 주로 JEDEC(Joint Electron Device Engineering Council, 국제반도체표준협의기구)과 SEMI에서 이루어지고 있다. JEDEC의 경우 3D 패키징, FOWLP, PLP, TSV 기술에 대한 직접적인 표준은 미흡한데 JEDEC의 분류 자체가 기술이 아닌 제품 즉, DRAM, Logic, Solid state memory 등으로 분류했기 때문이다. 이처럼 패키징 기술은 제품의 기술 속에 포함돼있어 직접적으로 표준이 제정되지는 않고 있는 상황이다.

수직 적층 반도체 표준을 주도하고 있는 JEDEC는 JC-42(solid-state memory) 위원회 내에서 수직 적층 반도체를 다루고 있다. JC-42.2는 TSV를 이용한 ‘tile’ 메모리를 연구하고 있고, JC-42.3은 메모리 제품 간의 wide IO 기술을 high bandwidth memory(HBM) 으로 규정해 JESD235 문서를 제안했다. JC-42.6은 메모리와 SoC간 wide IO를 JESD229 문서를 통해 규정하였다. JEDEC 에서 최근 차세대 패키징 관련 제정된 표준은 표2와 같다.

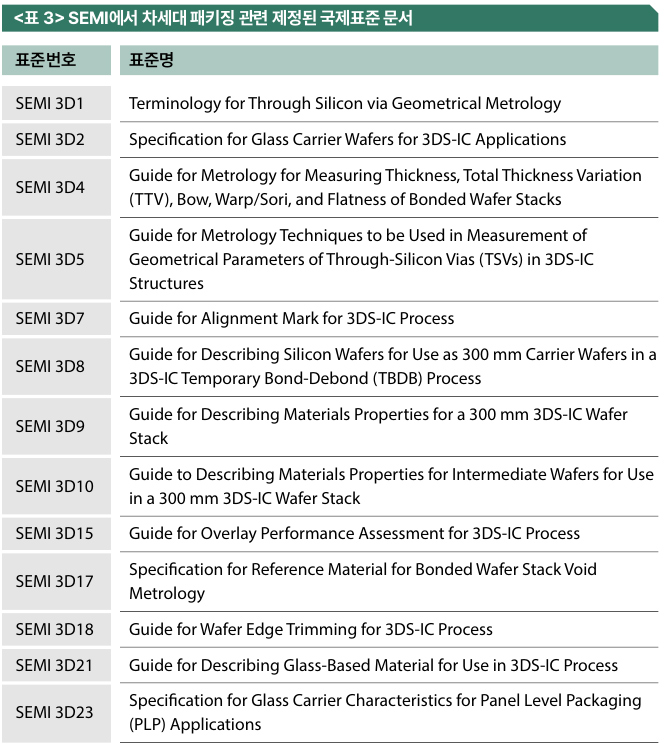

SEMI(Semiconductor Equipment and Materials International, 국제반도체장비재료협회)는 반도체 및 관련 산업의 주요 기업들로 이루어진 국제 산업 협회이며, 현재 실질적으로 관련 국제표준의 제정을 담당하고 있다. 특히 SEMI에서는 반도체 패키징과 관련된 ‘3D Packaging and Integration(3D 패키징 및 집적화) 위원회’를 운영하고 있으며, 해당 위원회를 통해 3D Packaging and Integration, 3DS-IC, Assembly & Packaging(조립 및 패키징) 관련 표준을 제정하고 있다.

3D Packaging and Integration committee에서는 3D 패키징과 관련된 전반적인 기술에 대한 표준을 진행하고 있으면 구체적으로는 아래와 같다.

- 장치와 패키징 간의 통신 링크를 제공하는 요소, 상호 연결 방식 및 고유한 패키징 어셈블리와 관련된 재료에 관련된 표준

- Fan-out/Fan-in Wafer Level Packaging, Panel Level Packaging, Three-Dimensional Stacking IC, Device Embedded Packaging, Flexible electronics 기술과 같은 이종 및 기타 멀티 칩 패키징 기술에 관한 표준

- 이러한 3D 통합 및 패키징 기술을 지원하는 측정 기술에 대한 표준

전체적으로 SEMI의 표준이 최근의 3D 패키징, FOWLP, PLP, 이종 접합 패키징 등 최신 기술에 대한 표준 제정에 좀 더 적극적으로 대응하고 있음을 알 수 있다.

SEMI에서 현재까지 차세대 패키징 관련 제정된 표준은 23건으로서 다른 표준기관에 비해 우위에 있으며, 대표적인 표준의 목차는 표3과 같다.

2030 표준 트렌드 전망

향후 미세피치 재배선(RDL)층과 TSV 등을 활용한 3차원적인 집적화 기술의 발달로 인해 아날로그/디 지털/RF/메모리 등의 조각 칩들을 재배선층을 통해 재조립하는 칩렛 기반 시스템 피키지 기술에 대한 연구개발이 활발하게 전개될 전망이다. 이러한 칩렛 기반 시스템 패키징은 기존의 SiP나 PoP 보다 훨씬 뛰어나고 이상적인 SOC에 근접한 우수한 시스템 성능을 제공하기 때문에 차세대 지능형 반도체 발전의 중요한 축으로 역할을 할 것으로 기대되고 있다.

칩렛 기반 시스템 패키지 안에서는 칩렛들이 수평/수직 방향으로 매우 가까이 배치돼 있어서 칩렛에서 발생하는 열이 효율적으로 제거되지 못하면 주위에 있는 다른 칩들에 열적 피해를 전가할 수 있다. 또한 시스템 패키지의 경우 신호의 무결성과 EMI/EMC 최적화를 기반으로 배치된 칩렛의 구조 설계가 매우 중요하며, 이 시점에서 구조 설계에 대한 국제표준이 핵심적으로 자리 할 수 있음을 알 수 있다.

한편 Fan-Out(FO) 패키징 기술은 반도체집적회로 기술과 유사한 영역으로 미래의 회로설계는 다이(die) 영역에 그치지 않고 Fan-Out 패키지 영역까지 포함하고 있는 실정이다. 특히 Heterogeneous Integration 분야는 여러 개의 다이들을 포함하는 시스템 설계의 영역으로 확장될 예정이며, 차세대 시스템반도체 성능의 최적화는 SoC 집적회로 다이 내부에 머무르지 않고 HI 영역에까지 확장하여 개발이 진행되고 있다.

재배선(RDL) 층 피치의 미세화, 접합점의 기계적 안정성, 재배선층을 통한 전달 신호 및 전력전달의 무결 성, 제조 및 사용환경에서의 RDL 층의 신뢰성 등 재배선층의 규격이나 성능지표 및 평가방법 등 다양한 기술들이 FO-PKG 형태의 시스템반도체의 특성과 밀접한 관련이 있어 향후 표준화가 반드시 필요하다.

Fan-Out 패키지 공정을 위한 웨이퍼 수준 혹은 패널 수준의 패키징 기술과 관련해 패널이나 캐리어의 세대별 크기 규격이나, 웨이퍼나 패널의 휘어짐을 방지하고 휘어진 정도를 평가하는 표준화된 평가방법, 웨이퍼와 RDL과의 정렬 기술, 접합력 향상 기술 등의 원천 기술과 개발된 기술들의 표준화가 반도체 기업 및 반도체 패키징 기업인 OSAT 기업들의 국제적인 협력을 위해 절실히 요구되고 있는 실정이다. 결론적으로 칩렛 기반 이종집적 시스템 패키지 기술을 개발하기 위해서는 이종집적 회로들과 RDL 및 TSV를 포함하는 모델링 및 설계 플랫폼을 구축하는 것이 필요할 것으로 판단된다.

국내 산업 경쟁력 강화를 위한 기술개발 연계 표준화 필요

차세대 반도체 패키지는 국내에서는 기초원천을 넘어 양산화 발전단계에 있기 때문에 확보된 FO-PKG, Chiplet, Heterogeneous Integration(이종접합) 기술을 집중적으로 연구함과 동시에 핵심 기술을 표준에 반영하기 위해 적극적인 시도를 이어가야 한다.

Heterogeneous Integration을 완성하기 위해서는 다양한 소재와 장비가 새롭게 개발돼야 하며 이를 위해서는 반도체 시스템부터 소재·부품·장비 그리고 산업계·학계·연구 분야의 생태계가 조성돼야 한다.

특히 삼성전자, 하이닉스, OSAT 업체, 소재·장비 업체 및 핵심 기술을 보유한 산·학·연의 협력과, 이를 활용한 표준소재, 표준장비를 개발 및 양산화 적용이 가능하다고 판단된다.

핵심기술을 보유한 국내 소·부·장 및 산·학·연이 반도체 패키지 생태계에서 heterogeneous integration 관련 상용 기술의 적기 개발이 가능하다면, 국내 첨단 패키지 개발 기술의 표준 기술화의 적기라고 판단 된다. 특히 이를 위해 기술 선점 및 국제표준화를 목표로 하는 국내 기관 대상 R&D 전주기에 걸친 표준특허 전략 제공, 고부가가치 표준특허 창출 지원이 필요할 것으로 판단된다. 끝으로 국내외 표준 제정을 위해 IEC와 ISO에 존재하는 유관 위원회 및 해외국가와의 협업을 통해 해당 표준화가 진행돼야 할 것으로 사료된다.